## Vertical System Integration by Using Inter-Chip Vias and Solid-Liquid Interdiffusion Bonding

Armin KLUMPP, Reinhard MERKEL, Peter RAMM\*, Josef WEBER and Robert WIELAND

Fraunhofer Institute for Reliability and Microintegration, Munich Division, Hansastrasse 27d, 80686 Munich, Germany

(Received October 27, 2003; revised February 17, 2004; accepted April 15, 2004; published xxxx yy, zzzz)

A new approach for 3D system integration, called Inter Chip Via-Solid Liquid Interdiffusion (ICV-SLID) is introduced. This is a new chip-to-wafer stacking technology which combines the advantages of the Inter Chip Via (ICV) process and the solid-liquid-interdiffusion technique (SLID) of copper and tin. The fully modular ICV-SLID concept allows the formation of multiple device stacks. A test chip was designed and the total process sequence of the ICV-SLID technology for the realization of a three-layer chip-to-wafer stack was demonstrated. The proposed wafer-level 3D integration concept has the potential for low cost fabrication of multi-layer high-performance 3D-SoCs and is well suited as a replacement for embedded technologies based on monolithic integration. [DOI: 10.1143/JJAP.43.dummy]

KEYWORDS: solid-liquid-interdiffusion, modular, multilayer, stack, copper, tin, tungsten, plugs, ultra-thin

Worldwide several outstanding technologies for 3D system integration are currently in development, a few of them are already in production. Successful market entry is determined by the performance improvement achieved and the profitability in relation to the total system cost. Manufacturing technologies based on wafer fabrication processes show the potential of a comparatively favorable cost structure. On the other hand wafer yield and chip area issues may speak against wafer stacking concepts. In consequence, chip-to-wafer technologies largely relying on wafer-level processes utilizing known good dice only, will be of advantage. A corresponding new approach for vertical system integration is introduced and discussed. This socalled inter-chip vias and solid-liquid interffusion (ICV-SLID) technology is based on adjusted bonding and vertical metallization of completely processed device substrates without interfering the basic IC process. First evaluations of interconnect delays and electromagnetic coupling (cross talk) gave no restrictions for high speed applications.

Vertical system integration based on direct InterChip Vias (ICV) with lateral dimensions of a few microns, leads to a very high integration density of the inter-chip wiring of stacked devices. Modeling of the signal interconnection structure of vertical integrated ICs shows that the ICVs will not degrade signal transmission.<sup>3)</sup> So the integration of complex high performance systems can be realized on a single stack of chips.

Corresponding concepts in principle are suitable for both, wafer stacking and chip-to-wafer stacking. Thinned device substrates (wafers or dice, respectively) are stacked by aligned bonding and electrically interconnected by free positioned inter-chip vias. Fraunhofer IZM in cooperation with Infineon Technologies developed a wafer-to-wafer stacking technology based on low temperature bonding with polyimide as intermediate layer and a vertical wiring using W- or Cu-filled inter-chip vias. Wafer stacks fabricated according to the so-called InterChip Via technology showed a very high vertical interconnect density of some 10<sup>5</sup> cm<sup>-2</sup> with low contact resistance inter-chip vias in the range of 1-3 Ohm. Although the reported results are promising<sup>1,2)</sup> wafer yield and chip area issues in general may speak against wafer stacking concepts: Yield loss by stacking of a non functional die to a good die, and even more serious, different

Fig. 1. Vertical System Integration; wafer-to-wafer versus chip-to-wafer stacking concept for fabrication of vertical integrated systems.

step sizes and chip sizes (with loss of active silicon area), result in an increase of the total cost per 3D-stack. In figure 1 wafer-to-wafer and chip-to-wafer concepts for vertical system integration are shown in principle. A chip-to-wafer stacking approach was reported by Infineon Technologies and Fraunhofer IZM.<sup>3)</sup> Both, the mechanical and the electrical connections between the chips are realized by solid-liquid-interdiffusion<sup>4)</sup> of thin electroplated Cu/Sn layers. This face-to-face technology has the potential for low cost fabrication but on the other hand - as non-modular concept - is limited to applications with two layer stacks.

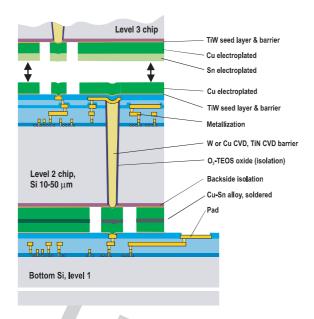

In consequence we are working on the development of a new chip-to-wafer stacking technology which combines the advantages of the ICV process and the solid-liquid-interdiffusion technique (SLID). The fully modular ICV-SLID concept allows the formation of multiple device stacks. The schematic cross section of a corresponding 3D integrated circuit is shown in Fig. 2. Aligned stacking of a 3rd level chip is also indicated in the figure. The starting materials for the chip-to-wafer approach ICV-SLID are completely processed and tested device wafers. For a first evaluation a test chip with 3D integrated structures was designed in order to characterize the inter-chip interconnections. 200 mm wafers with metallization layers and inter-level dielectrics were processed according to the ICV-SLID process flow. First step of the 3D integration sequence is the formation of inter-chip vias by deep trench etching, lateral isolation and

Wafer-to-Wafer

Chip-to-Wafer

Planar K. Technologies

Thinning and Bonding

InterChip Metalization

Chip-to-Wafer

Waferscale Processing

(complete IC-labrication)

Chip-to-Wafer

Aligned Bonding

Separation

Waferscale Processing

(interChip Metalization)

Dixing Packaging

<sup>\*</sup>E-mail address: peter.ramm@izm-m.fraunhofer.de

Fig. 2. Schematic cross section of a corresponding 3D integrated circuit with the fully modular ICV-SLID concept.

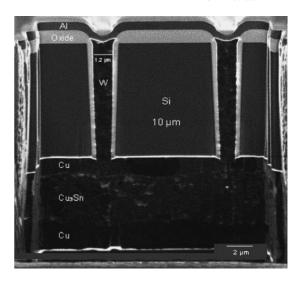

metal filling. Typically 1-3 µm diameter vias are prepared on the top wafer. These high aspect ratio ICVs are etched through all dielectric layers and typically 12 µm deep into the silicon. The via trench is laterally isolated with highly conformal O<sub>3</sub>/TEOS and finally refilled with TiN/W CVD. Subsequently, a tungsten etch back process is applied for Wplug formation. The lateral electrical connection of the metallized inter-chip via with the metal level of the top wafer is done by opening contact windows on the top wafer followed by a standard Al metallization and passivation. The wafer is then temporarily bonded onto a handling substrate by using a glue polymer and thinned with high uniformity until the ICVs are opened from the rear (remaining silicon thickness approximately 10 µm). Through-mask electroplating of a typically 8 µm thin copper/tin bilayer is applied onto the backside of the thinned Wafer. The bottom wafer is through-mask electroplated with Cu as the counterpart metal of the soldering metal system. A 3D integrated test structure after SLID and removal of the handling substrate is shown in Fig. 3.

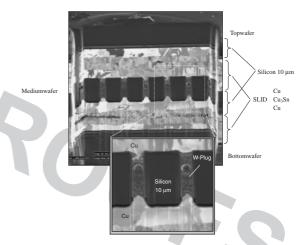

The device stack is now ready for addition of the 3rd level chip (principle shown in Fig. 2). The process sequence is identical to the one used for the 2-layer-stack, for the process concept is completely modular. Figure 4 shows the cross section (FIB) of a three-layer stack. In this sample the top layer is mounted up-side-down on top of the medium layer and carries no additional interchip vias. The  $10\,\mu m$  thin medium chip is connected to the bottom device wafer by the SLID system (Cu, Cu<sub>3</sub>Sn  $\varepsilon$ -phase, Cu) as well and supplies the electrical interconnection between the bottom and the top layers. Finally the bond pads are opened and the 3D integrated device stack can be tested, separated and mounted by use of standard procedures.

A new approach for 3D system integration, is introduced. A test chip was designed and the total process sequence of the ICV-SLID technology for the realization of a three-layer chip-to-wafer stack was demonstrated. The proposed wafer-level 3D integration concept has the potential for low cost

Fig. 3. Cross section (FIB) of 2-level stack with ICV-pins,  $10\,\mu m$  silicon and SLID metal system.

Fig. 4. Cross section (FIB) of a three-layer stack at a electrical contact pin array.

fabrication of multi-layer high-performance 3D-SoCs and is well suited as a replacement for embedded technologies based on monolithic integration.

This report is partly based on a project which is supported by the German Bundesministerium für Bildung und Forschung under support-no. 01M 2999 A.

- P. Ramm, D. Bonfert, H. Gieser, J. Haufe, F. Iberl, A. Klumpp, A. Kux and R. Wieland: *Proc. Int. Interconnect Technology Conf. (IITC 2001)*, (2001) p. 160.

- P. Ramm, D. Bonfert, F. Iberl, A. Klumpp, S. Riedel, S. E. Schulz, R. Wieland, M. Zacher and T. Gessner: *Proc. Advanced Metallization Conference (AMC 2001)*, eds. A. J. Mckerrow *et al.* (Material Research Society, Pittsburgh, 2001), Mater. Res. Soc. Proc. V-17, p. 159.

- H. Huebner, O. Ehrmann, M. Eigner, W. Gruber, A. Klumpp, R. Merkel, P. Ramm, M. Roth, J. Weber and R. Wieland: *Proc. Advanced Metallization Conf. (AMC 2002)*, eds B. M. Melnick *et al.* (Material Research Society, Pittsburgh, 2002) Mater. Res. Soc. Proc. V-18, p. 53.

- L. Bernstein and H. Bartolomew: Trans. Met. Soc. AIME 236 (1966) 404.

- S. A. Kuehn, M. B. Kleiner, P. Ramm and W. Weber: IEEE Trans. Comp., Packag., Manufact. Technol.-Part B, Vol. 19, No. 4, (1996) p. 71.